# Разработка высокоскоростного цифрового десериалайзера на транзисторах Е-типа, на гетероструктурах арсенида галлия.

#### А.Х. Курбанов, Б.В. Калинин

ООО «Микровейв АйСи»

**Аннотация**: Данная работа посвящена проблематике создания цифровых схем управления СВЧ устройствами, сделанных по технологии GaAs.

Описаны, достоинства использования, встроенного в кристалл высокоскоростного цифрового десериалайзера разработанного для GaAs технологии.

Также в данной работе, рассматриваются решения по уменьшению занимаемой площади конечного устройства.

**Ключевые слова**: GaAs, цифровые устройства, десериалайзер.

### 1. Введение

В СВЧ электронике, подавляющее число разработчиков, имеющих дело с GaAs технологией, сосредоточено на проектировании аналоговых трактов и мало кто берётся создавать быстродействующие цифровые устройства. В качестве управляющих цифровых трактов для СВЧ приёмо-передающих модулей, применяются иностранные чипы. Встраивание цифровой части внутрь монолитной интегральной СВЧ схемы дополнительно даёт экономию в площади конечного устройства. На рынке существует огромный спрос на свои быстродействующие, сериалайзеры, десериалайзеры, ЦАП, АЦП и другие цифровые устройства.

В отличие от кремниевой технологии, в технологии GaAs отсутствуют транзисторы р-типа. В ней присутствую только транзисторы п-типа с индуцированным каналом (Е-тип) и со встроенным каналом (D-тип). Это накладывает существенные ограничения при разработке цифровых устройств.

## 2. Десериалайзер

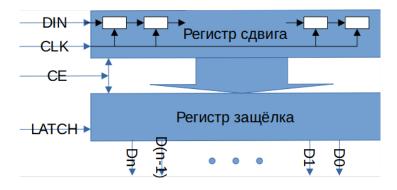

Идея разработки десериалайзера была взята из технического описание на готовое коммерческое устройство [1]. Десериалайзер — это устройство, которое позволяет преобразовать набор последовательных бит в параллельный. Структурно [1, 2] он состоит из двух регистров: сдвига и защёлки (рис. 1).

Рисунок 1. Структурная схема десериалайзера.

При высоком уровне сигнала на входе CE разрешена работа десериалайзера. Входные данные DIN записываются в регистр сдвига, синхронно тактируемые сигналом

CLK. За один такт CLK происходит сдвиг данных в следующую ячейку памяти сдвигового регистра. Когда все данные записаны в регистр сдвига, сигнал CLK переходит в низкое состояние. По высокому сигналу LATCH, происходит копирование всех данных в регистр защёлку. Сброс обоих регистров происходит по низкому сигналу CE.

Общее количество управляющих сигналов во входном интерфейсе десериалайзера – четыре. Ширина выходной шины десериалайзера ограничена только током потребления устройства. Поэтому, выгода от применения десериалайзера становится очевидной при количестве входных сигналов управления более четырёх. Более того, использование десериалайзера позволяет улучшить помехозащищённость канала связи.

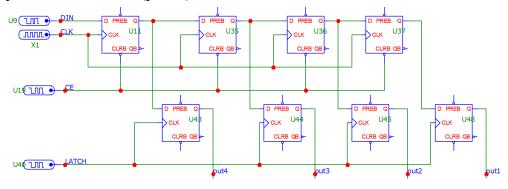

Электрическая схема, предлагаемая для реализации десериалайзера на D-триггерах, показана ниже (рис. 2).

Рисунок 1. Схема четырёхбитного десериалайзера на D-триггерах.

## 3. Моделирование логики работы десериалайзера в МісгоСар

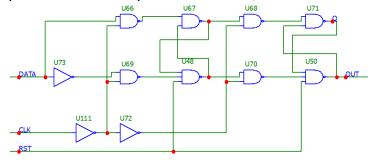

Для реализации регистров в десериалайзере, необходимо разработать синхронный D-триггер. Моделирования логики работы было сделано в САПР MicroCap. В публикации [2] описано схемотехническое решение по созданию двухступенчатого синхронного D-триггера из логических примитивов: NOT, 2NAND и 3NAND (рис. 3).

Рисунок 2. Схема двухступенчатого D-триггера на логических примитивах.

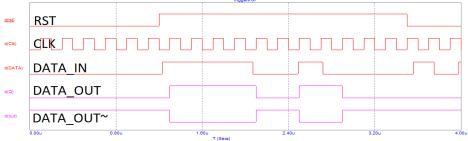

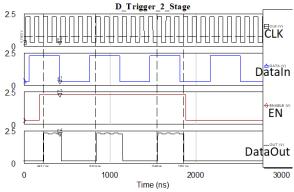

На осциллограммах (рис. 4) видно, что входные данные DATA\_IN, поступают на выход двухступенчатого D-триггера DATA\_OUT, синхронно с передним фронтам сигнала CLK только при наличии высокого уровня сигнала RST. Логика работы соответствует описанной, в предыдущем пункте.

Рисунок 3. Моделирование работы двухступенчатого D-триггера.

## 4. Моделирование десериалайзера в AWR

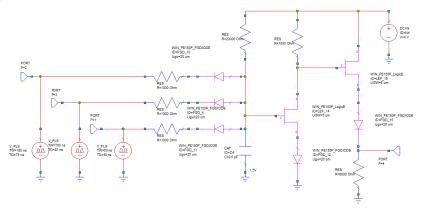

За основу логического примитива была взята диодно-транзисторная логика (ДТЛ) [3, 4] (рис 5).

Рисунок 4. Схема логического элемента 3NAND.

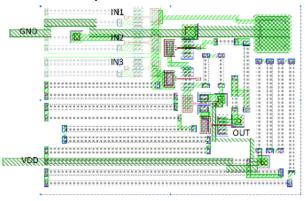

Для проектирования двухступенчатого D-триггера на GaAs, требуется разработать 3NAND (трёх входовый И-НЕ). Схема содержит 5 диодов и 2 транзистора. На (рис. 6) представлена топология 3NAND примитива.

Рисунок 5. Топология логического элемента 3NAND.

**Таблица 1.** Таблицы истинности элементов 3NAND, 2NAND, NOT

| 3NAND |      |      |     |  |

|-------|------|------|-----|--|

| IN_1  | IN_2 | IN_3 | OUT |  |

| X     | X    | X    | 1   |  |

| 1     | 1    | 1    | 0   |  |

| 2NAND |      |     |  |  |

|-------|------|-----|--|--|

| IN_1  | IN_2 | OUT |  |  |

| X     | X    | 1   |  |  |

| 1     | 1    | 0   |  |  |

| NOT |     |  |  |

|-----|-----|--|--|

| IN  | OUT |  |  |

| 1   | 0   |  |  |

| 0   | 1   |  |  |

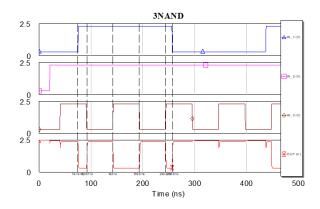

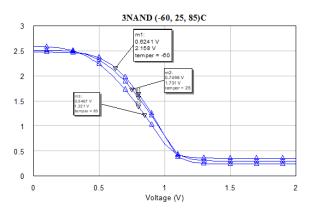

При наличии на всех входах логического элемента 3NAND логической «1», на его выходе устанавливается логический «0». Осциллограммы логики работы (рис. 7) логического элемента 3NAND и его передаточная характеристика при температурах -60, +25, +85 °C (рис. 8) показаны ниже.

Рисунок 6. Моделирование логического элемента 3NAND

Рисунок 7. Передаточная характеристика 3NAND от температуры

Для конструирования двухступенчатого D-триггера (рис. 3), необходимо получить элементы 2NAND и NOT. Для получения из 3NAND логического элемента 2NAND задействуют два любых входа элемента 3NAND. Для получения логического элемента NOT задействуют один любой вход элемента 3NAND. Не используемые входы, никуда не подключаются, это основное преимущество ДТЛ.

Рисунок 8. Моделирование работы двухступенчатого D-триггера

На осциллограммах (рис. 9), можно видеть логику работы D-триггера. Входной сигнал DataIn, поступает на вход устройства. При высоком уровне сигнала EN даётся разрешение работы. При появлении, после этого переднего фронта сигнала CLK, про-исходит запись входных данных DataIn в DataOut. Другими словами, D-триггер копирует значение с DataIn на DataOut по переднему фронту тактового импульса CLK и помнит это состояние всё остальное время, пока сигнал EN равен «1» [5]. Двухступенчатый D-триггер является синхронным.

Имея в распоряжении двухступенчатый синхронный D-триггер, можно спроекти-

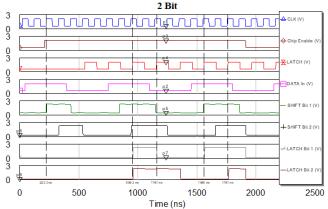

ровать один бит десериалайзера, который состоит из регистра сдвига и регистра защёлки. Далее регистры сдвига соединяются между битами последовательно. На осциллограмме (рис. 10) показана работа двух битов десериалайзера. На ней видно, что в регистре сдвига, данные DATA продвигаются как сигналы: Shift bit1, SHIFT bit 2, с каждым передним фронтом сигнала CLK. Сигналы: LATCH bit1, LATCH bit2, фиксируются на выходах десериалайзера по переднему фронту сигнала LATCH.

Рисунок 9. Моделирование работы 2-ух битов десериалайзера

При разработке топологии десериалайзера необходимо минимизировать индуктивные и ёмкостные паразитные связи [6].

3 \* Версия 1 2 Ед. изм. Кол-во транзисторов/диодов 60/0 48/120 114/0 шт. 120/0 Tok +/-21.3/0 25/18 мА +4/-4Напряжение питания +4 +4 В 73 Задержка распространения 10 2.3 нС 22/16 0.2/0.2Время Фронта/Спада 3/3 нС 1000 Мб/С Максимальная скорость 5 67 1.3x0.30.38x0.19 Габариты MM

Таблица 2. Расчётные значения 1 бита десериалайзера

#### 5. Заключение.

Использование десериалайзера снижает количество сигналов управления до 4 и обладает лёгкой масштабируемостью, что уменьшает количество разварок и увеличивает надёжность всей системы. Повышается общая помехозащищённость канала управления. Реализации на GaAs технологии, позволяет встраивать его непосредственно в топологию кристалла, что минимизирует площадь конечного устройства.

#### Список литературы:

- 1. Datasheet «6-bit X-Band Core chip» // OMMIC company, 2021, 13 crp.

- 2. Касьянов А.Н. «МісгоСар в схемотехнике»// ТГТУ, 2004, 81 стр.

- 3. Хоровиц П., Хилл У. «Искусство схемотехники 1»// Мир. 1983, 598 стр.

- 4. Хоровиц П., Хилл У. «Искусство схемотехники 2»// Мир. 1983, 590 стр.

- 5. Дэвид М. Харрис и Сара Л. Харрис «Цифровая схемотехника и архитектура компьютера» // Morgan Kaufman, 2013, 1662 стр.

- 6. Howard J. Martin G. «High speed digital design»// Person, 1993, 464 стр.

<sup>\*</sup> в разработке